# $\overline{\text{MS}}60801\overline{\text{IP}}$

# Prime Number Interleaver IP Module (Verilog-HDL)

## ■概要

MS60801IPは3GPPに準拠した素数インターリーバIPモジュールです。時系列的にリニアにアドレス格納する入力データを保存するDPRAMのインターリーブした後のリードアドレスを生成します。

# ■ 特長

- ●3GPP TS 25.212 V7.3.0 に準拠

- ●入力信号: CLK, XRST, BLKSIZE[12:0], INIT\_TRG, ILRD\_TRG

- ●INIT\_BUSY 端子により内部回路の初期化中を通知

- ●INIT\_TRG 信号により初期化演算開始

- ●ILRD\_TRG 信号によりインターリーブアドレス出力開始

- ●出力信号: INIT\_BUSY, RD2\_AD[12:0], RD2\_ENB, SFT2\_ENB

#### ■ 入出力信号

| 信号名           | I/O | 極性 | 信号説明                                        |  |  |  |

|---------------|-----|----|---------------------------------------------|--|--|--|

| CLK           | I   | P  | Clock                                       |  |  |  |

| XRST          | I   | L  | Reset Signal Input Low Active               |  |  |  |

| INIT_TRG      | I   | Н  | Initialize Start Trigger Signal Input       |  |  |  |

| ILRD_TRG      | I   | Н  | Interleaver Read Start Trigger Signal Input |  |  |  |

| BLKSIZE[12:0] | I   | Н  | Block Size (K number) Input (40≦K≦5114)     |  |  |  |

| INIT_BUSY     | О   | Н  | Initialize Sequence Busy Signal Output      |  |  |  |

| RD2_AD[12:0]  | О   | Н  | Interleaver Data RAM Read Address output    |  |  |  |

| RD2_ENB       | О   | Н  | Read Enable Signal Output                   |  |  |  |

| SFT2_ENB      | О   | Н  | 3 Clock Delay Signal after RD2_ENB          |  |  |  |

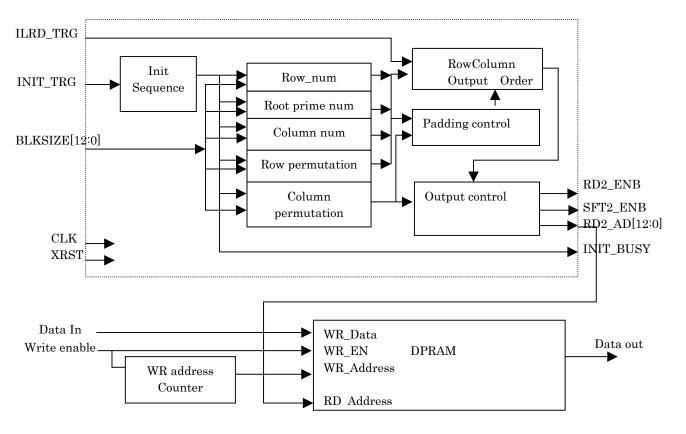

# ■ ブロック図

\*点線内が本 IP のブロック図です。点線外は外部回路を構成する必要があります。

# ■ 動作説明

インターリーバに入力されるデータは入力されるビット系列の大きさによって行列の大きさが決定される行列に、順次ビット系列として入力される。入力されたビット系列は素数インターリーバ法により行列の順序を入れ替えて 出力される。

- 1) INIT TRG が入力されると BLKSIZE(K) 及び内部テーブルデータをもとに以下を算出する初期化処理を行う。

- ・ 使用する行列の行数 (R)

- 使用する素数(p)

- ・ 使用する基底数(v)

- 使用する行列の列数(C)

- · 行内の基準配列(s)

- 2) 内部回路が上記の算出状態にある期間 INIT\_BUSY 信号に High を出力する。

- 3) 初期化処理が終了するとインターリーブ後のリードアドレス出力スタンバイ状態となり、この状態で ILRD\_TRG 信号が入力されるとリードアドレス出力が開始される。

- 4) 初期化で求めた値及び内部テーブルを使用してデータ出力行列を想定してインターリーブ後の出力アドレスを出力する。

#### ■ タイムチャート

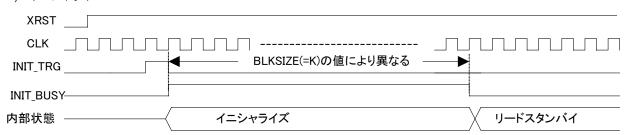

## 1) イニシャライズ

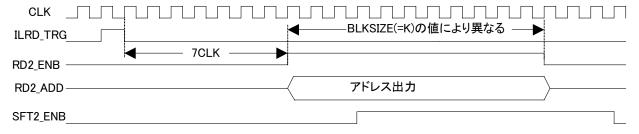

# 2) アドレス出力

- インターリーブ処理の詳細

- 1. 入力ビットシーケンスの行列への入力

ビットシーケンス  $x_1, x_2, x_3, ..., x_K$  が以下で示される行列に入力される。

(1) 行列の行数 *R* は以下の式で決められる。

$$R = \begin{cases} 5, & \text{if } (40 \le K \le 159) \\ 10, & \text{if } ((160 \le K \le 200) \text{ or } (481 \le K \le 530)) \\ 20, & \text{if } (K = \text{any other value}) \end{cases}$$

行は上から下こ0, 1, ..., R - 1とナンバリングされる。

(2) p を求める。

以下の特殊条件のときは一義的に下式となる。

if  $(481 \le K \le 530)$  then

$$p = 53$$

and  $C = p$ .

そのほかのときは最小の素数 p を Table 1 から以下の式で探す。

$$K \leq R \times (p+1),$$

求めたpから以下の式で列数Cを求める。

$$C = \begin{cases} p-1 & if \quad K \leq R \times (p-1) \\ p & if \quad R \times (p-1) < K \leq R \times p \\ p+1 & if \quad R \times p < K \end{cases}$$

列は 左から右に0, 1, ..., C - 1 とナンバリングされる。

- (3) ビットシーケンス  $x_1, x_2, x_3, \dots, x_K$  を上記  $R \times C$  の行列に以下のように入れる。:

- 入力行列

**なお、** $R \times C > K$  のときは K+1 番目以降( $k = K + 1, K + 2, ..., R \times C$ .)のデータはダミービットでパディング される。なお、ダミービットは出力されるときに取り除く。

Table1: 素数 pとそれに関系する初期底 v のテーブル

| р  | V | р  | V | р   | V | р   | V  | р   | V |

|----|---|----|---|-----|---|-----|----|-----|---|

| 7  | 3 | 47 | 5 | 101 | 2 | 157 | 5  | 223 | 3 |

| 11 | 2 | 53 | 2 | 103 | 5 | 163 | 2  | 227 | 2 |

| 13 | 2 | 59 | 2 | 107 | 2 | 167 | 5  | 229 | 6 |

| 17 | 3 | 61 | 2 | 109 | 6 | 173 | 2  | 233 | 3 |

| 19 | 2 | 67 | 2 | 113 | 3 | 179 | 2  | 239 | 7 |

| 23 | 5 | 71 | 7 | 127 | 3 | 181 | 2  | 241 | 7 |

| 29 | 2 | 73 | 5 | 131 | 2 | 191 | 19 | 251 | 6 |

| 31 | 3 | 79 | 3 | 137 | 3 | 193 | 5  | 257 | 3 |

| 37 | 2 | 83 | 2 | 139 | 2 | 197 | 2  |     |   |

| 41 | 6 | 89 | 3 | 149 | 2 | 199 | 3  |     |   |

| 43 | 3 | 97 | 5 | 151 | 6 | 211 | 2  |     |   |

# 2. 行内及び行間の順列

$R \times C$  の行列に入力ビットシーケンスが格納された後に以下の(1)~(6)のステップのアルゴリズムで行内、行間の順序付けが実行される。

- (1) Table 1 から計算された pに相当する基底数 v を選択する。.

- (2) 行内の順列として以下のように基準配列  $\left\langle s(j) \right

angle_{j \in \{0,1,\cdots,p-2\}}$  を構成する。

$$s(j) = (v \times s(j-1)) \mod p$$

,  $j = 1, 2, ..., (p-2), \text{ and } s(0) = 1$ .

mod はモジュロを表す。(mod7は"7"を法とする演算、すなわち7で割り算をした余りに相当する。)

- (3) 最初の素数を $q_0 = 1$  として  $\left\langle q_i \right\rangle_{i \in \{0,1,\cdots,R-1\}}$  の素数シーケンスを $q_i$  と p-1の最大公総数が1かつ  $q_i > 6$ 、かつ  $q_i > q_{(i-1)}$  として  $i=1,2,\ldots,R-1$ について求める。

- (4) 上記で計算された $\left\langle q_{i} \right\rangle_{i \in \{0,1,\cdots,R-1\}}$  を使用して以下の式により $\left\langle r_{i} \right\rangle_{i \in \{0,1,\cdots,R-1\}}$  を求める。  $r_{T(i)} = q_{i}, \quad i = 0,\,1,\,\ldots,R$   $1,\,\ldots$

ここで  $\left\langle T(i) \right

angle_{i \in \{0,1,\cdots,R-1\}}$  は入力されたKの値こよりTable~2により決定される。

Table 2: インターリーバの行間の順列

| Number of input bits                               | Number    | Inter-row permutation patterns                                         |

|----------------------------------------------------|-----------|------------------------------------------------------------------------|

| K                                                  | of rows R | < <i>T</i> (0), <i>T</i> (1),, <i>T</i> ( <i>R</i> - 1)>               |

| (40 ≤ K ≤ 159)                                     | 5         | <4, 3, 2, 1, 0>                                                        |

| $(160 \le K \le 200)$ or $(481 \le K \le 530)$     | 10        | <9, 8, 7, 6, 5, 4, 3, 2, 1, 0>                                         |

| $(2281 \le K \le 2480)$ or $(3161 \le K \le 3210)$ | 20        | <19, 9, 14, 4, 0, 2, 5, 7, 12, 18, 16, 13, 17, 15, 3, 1, 6, 11, 8, 10> |

| K = any other value                                | 20        | <19, 9, 14, 4, 0, 2, 5, 7, 12, 18, 10, 8, 13, 17, 3, 1, 16, 6, 15, 11> |

(5) 行が i = 0, 1, ..., R - 1 のときの行内の j 番目の順列は \*もし(C = p) のときは

$$U_i(j) = s((j \times r_i) \mod(p-1)), \quad j = 0, 1, ..., (p-2), \text{ and } U_i(p-1) = 0,$$

ここで  $U_i(j)$  はもとの j 列 i 行のビット位置を示す。

\* (C = p + 1) のときは

$$U_i(j) = s((j \times r_i) \mod(p-1)), \quad j = 0, 1, ..., (p-2). \quad U_i(p-1) = 0, \text{ and } U_i(p) = p,$$

となる。但し、もし  $(K = R \times C)$  となるときは  $U_{R-1}(p)$  と  $U_{R-1}(0)$  を交換する。

\* (C = p - 1) のときは

$$U_i(j) = s((j \times r_i) \mod(p-1)) - 1, \quad j = 0, 1, ..., (p-2),$$

となる。

(6) 行間の順列を Table 2 に示す  $\left\langle T(i) \right\rangle_{i \in \{0,1,\cdots,R-1\}}$  により行う。 ここで T(i) は元の j 番目 の行を表す。

# 3. 行列からのビットデータ出力

上記で変更された行列を下図に対象として示すようにナンバリングしてナンバリングの順番に従って出力する。

$$\begin{bmatrix} y'_1 & y'_{(R+1)} & y'_{(2R+1)} & \cdots y'_{((C-1)R+1)} \\ y'_2 & y'_{(R+2)} & y'_{(2R+2)} & \cdots y'_{((C-1)R+2)} \\ \vdots & \vdots & \vdots & \cdots & \vdots \\ y'_R & y'_{2R} & y'_{3R} & \cdots & y'_{C\times R} \end{bmatrix}$$

但し入力データ行列でパディングされたビットは出力時に取り除いて出力する。従ってパディングされたビットが存在するときには取り除かれるビット数は  $R \times C-K$ となる。

## 参考

- [1] 3GPP TS 25.212 V7.3.0 (2006-12) 3<sup>rd</sup> Generation Partnership Project; Technical Specification Group Radio Access Network; Multiplexing and channel coding(FDD)(Release 7)

- 1.本書に記載された内容につきましては、改善のため予告なしに変更することがあります。

- 2.本書に記載された情報や図面等の使用に起因した等三者の所有する工業所有権およびその他の権利侵害に対し当社はその責任を負うものではありません。

- 3.本書に記載された内容を当社に無断で転載または複製することは、ご遠慮下さい。

- 4.本書に記載された製品は「外国為替及び外国貿易管理法」に基づく戦略物質等に該当します。従って本製品を輸出する場合は、同法に基づく許可が必要となります。

〒407-0014 山梨県韮崎市富士見 3-16-37 TEL 0551-23-0575 FAX 0551-23-0576 <a href="http://www.megasys.co.jp/">http://www.megasys.co.jp/</a>

© 2008 Mega-Sys Co, Ltd.